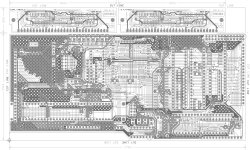

Rev B of NoCan3:

This may be the final NoCan3 design, NoCan3-B.

Testing will tell the story, and it all works.

No basic electronic changes. Plenty of layout changes, especially the

BLKx jumper positions.

Folks are suggesting that another MAX232 be added to allow all RS-232

pins accessable (except RI). Give me feedback on this:

(For the Lattice-2096 boards that are out there, this can be added)

1. It has $FF90 Bit 3 toggling (Vector page @ $FFEX), it fits into the

CPLD. This mirrors the GIME bit and sets the CPLD accordingly.

(Curtis, you have this.)

Bit 0: 4MHz enable, disable.

FAST jumper must be installed

(4mhz = OFF) to set or reset the 4MHz bit in software.

0 = off, no 4MHz.

1 = on, 4MHz on, but only if in 2MHz mode already.

Bit 1: Changes the 4MHz cycle from short to

long.

0 = Two cycles. Balanced fit between Q & E.

1 = Three cycles. UnBalanced fit. Makes E a little

bit shorter, Q unchanged from Two cycle setting.

Either 2 cycles of 28MHz

or 3 cycles of 28MHz in length. 34.9206ns per cycle.

short, 2 cycles = 7.159MHz. This is the frequency of the waveform, not

the through-put.

long, 3 cycles = 4.772MHz. ditto.

Bit 2: Turbo Phase.

Has the ability to shift the Turbo. This may help

others' coco's to use the Turbo mode.

0 = Normal.

1 = Shift.

What does this do?

It moves the Turbo position. Moves it right or left depending on which

GIME you have.