Práctica

Número 6

Diseño

de amplificadores multietapa con transistores bipolares y monopolares

Objetivo

Experimentar,

en la medida de lo posible, el comportamiento del amplificador

multietapa en las diferentes combinaciones existentes, tanto para la

alternativa de transistor BJT - BJT, como para la alternativa FET -

BJT; comprobar las características propias de cada posibilidad y

definir sus ventajas y desventajas.

Introducción [3]

El amplificador

multietapa

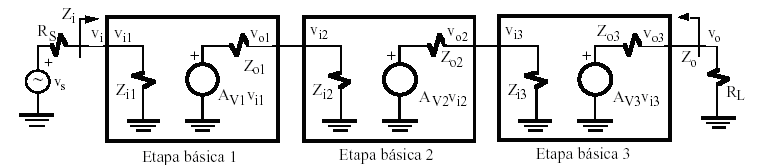

Un

amplificador

multietapa es un amplificador constituido por un conjunto de amplificadores básicos conectados en cascada. La técnica de análisis de este amplificador es sencilla ya que se reduce básicamente a analizar un conjunto de etapas básicas y a partir de sus modelos equivalentes (tensión o corriente) obtener el modelo equivalente del amplificador completo. El acoplo entre las etapas básicas puede ser realizado básicamente de dos maneras: directamente o acoplo DC y a través de un condensador. El primero exige estudiar conjuntamente la polarización de cada una de las etapas lo que complica su análisis en continua. Sin embargo, el amplificador multietapa carece de frecuencia de corte inferior. El acoplo a través de un condensador aísla en DC las etapas básicas a costa de introducir una frecuencia de corte inferior. Este último acoplo solo es usado en aquellos amplificadores realizados con componentes discretos.

Un aspecto

importante a tener en cuenta en amplificadores

multietapa, si se desea un amplificador de altas prestaciones, es el impacto del acoplo de impedancias entre los amplificadores

básicos. Como ejemplo, el amplificador

multietapa de la figura anterior está

constituido por: tres etapas

básicas representadas a través de su modelo en tensión, un circuito de entrada y una resistencia de carga. La impedancia de entrada del amplificador

completo es Zi=Zi1, es decir, la impedancia de entrada de la primera etapa, y su impedancia de salida Zo=Zo3 es la impedancia de salida de la última etapa.

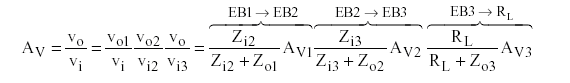

La expresión de la ganancia del amplificador,

teniendo en cuenta que vi=vi1, vo1=vi2, vo2=vi3

y vo3=vo,

es:

La ecuación anterior tiene varios términos. El primero indica la adaptación de impedancias entre la etapa básica 1 y la 2, el segundo entre la 2 y la 3, y el último entre la 3 y la resistencia de carga. Un buen amplificador en tensión debe tener, además de altos valores de AV1, AV2 y AV3, un acoplo de impedancias adecuado para que las fracciones de la ecuación anterior no reduzcan la ganancia de tensión a un valor muy bajo. Para ello, es condición necesaria que se verifique Zi2>>Zo1,

Zi3>>Zo2

y RL>>Zo3.

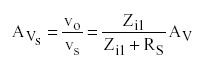

Extrapolando esta

condición se puede decir que un amplificador de tensión ideal debe verificar que AV→ inf, Zi.→ inf y Zo→0. Esta misma conclusión se obtiene si se analiza el circuito de entrada de forma que la ganancia en tensión referido al generador vs viene dada por:

La

ecuación anterior indica que para evitar una fuerte reducción en esta ganancia es necesario que Zi1>>RS.

Nótese que

si

RS>>

Zi1 entonces la

AVs.0.

Un análisis similar se puede realizar a un amplificador

multietapa de la siguiente figura basado en modelos equivalentes

de corriente de las etapas

básicas. Su impedancia de entrada es Zi=Zi1 y de salida Zo=Zo3. La expresión de la ganancia en corriente del amplificador,

teniendo en cuenta que ii=ii1, io1=ii2,

io2=ii3 y io3=io, es:

y

referida a is,

Un

buen amplificador en corriente debe tener, además de altos valores de AI1,

AI2

y

AI3,

un acoplo de impedancias adecuado. Para ello, es condición necesaria que se verifique Zi2

<<

Zo1,

Zi3

<<

Zo2,

RL<<

Zo3

y

Zi1<<RS.

Un amplificador de corriente ideal debe verificar que AI.→ inf,

Zi.→ 0

y Zo.→ inf.

Estas condiciones son antagonistas a las necesarias para un amplificador en tensión. Esto significa que un buen amplificador de corriente es un mal amplificador de tensión y, viceversa, un buen amplificador en tensión no puede ser de corriente.

Desarrollo

de la práctica

Material y equipo a emplear

- 2

transistores 2N2222

- 1 transistor 2N3370

- Potenciómetros de diversos

valores

- Resitencias de diversos valores

- 5 capacitores de 10 μF

- 1

generador de funciones

- 1

osciloscopio

- 1 multímetro

NOTA: Para el caso de esta

prática, todas las mediciones y experimentaciones se basan en el

transistor bipolar 2N2222, así como en el transistor monopolar

2N3370; si se desean ver las especificacioens del mismo,

puede consultarlas para el BJT

y para el FET.

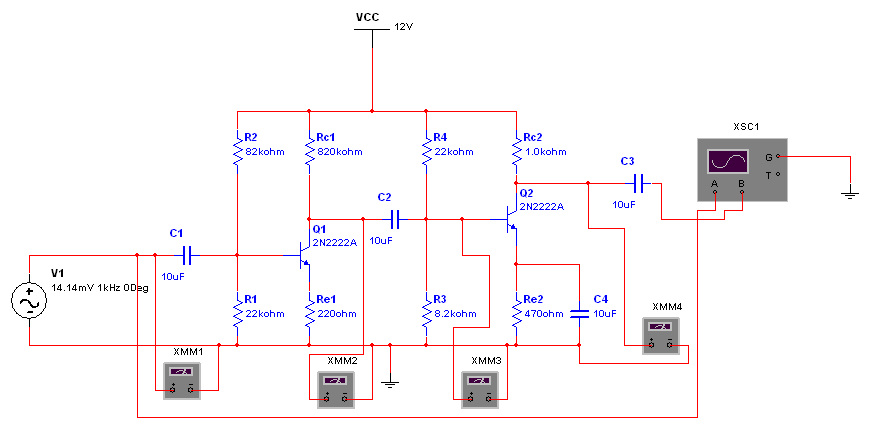

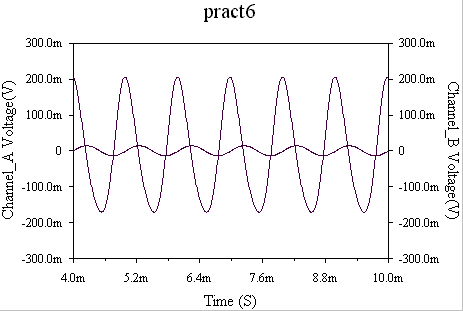

- Arme el circuito de la siguiente figura y aplique a la entrada

una señal sinusoidal de 1Khz. de frecuencia, iniciando con el

control de amplitud del generador de funciones en el mínimo;

aumentar lentamente hasta antes de que se empiece a distorsionar la

señal de salida.

Figura

1:

Diagrama de polarización del amplificador multietapa con dos

transistores bipolares

Figura

1:

Diagrama de polarización del amplificador multietapa con dos

transistores bipolares

- Cuantifique la ganancia de voltaje total y registre su valor.

Luego

de realizar la medición pertinente, se observó lo

siguiente en la señal de entrada como en la de salida:

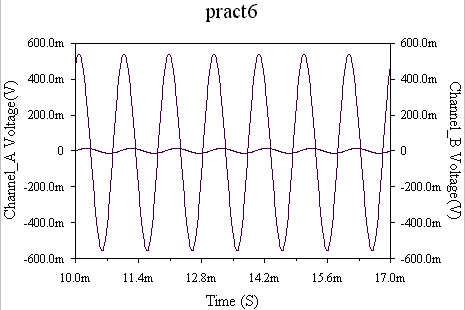

Por

lo cual obtenemos una ganancia de:

Ahora

bien, al observar la gráfica de la simulación, esta

ganancia parece no ser la indicada, debido, a como veremos a lo largo

de el desarrollo de esta práctica; a que el acoplamiento no

está trabajando perfectamente, por lo que al no estar acopladas

ambas fases, no podemos hablar de que tengamos una eficiencia completa,

sin embargo, la ganancia si resulta mayor que en prácticas

pasadas.

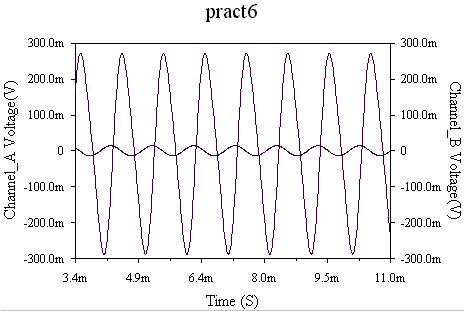

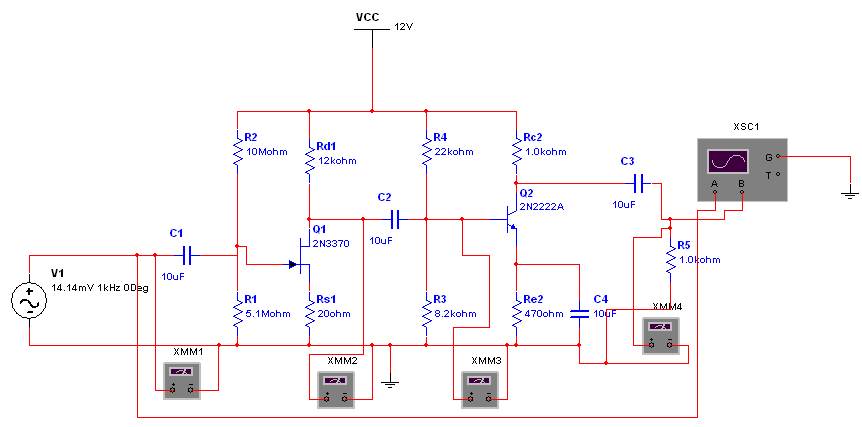

Figura

2:

Gráfica resultante de la simulación del circuito mostrado

en la figura número 1

- ¿Cómo es la fase y la simetría de la

señal de salida con respecto a la señal de entrada?

Aunque en la

simulación no se aprecia de esta manera, al momento de la

experimentación si se comprobó la importante

característica del amplificador que mantenía la

señal de salida en perfecta fase con respecto a la entrada;

mientras que, en el caso de la simetría, en ambos casos se

obtuvo sin problema.

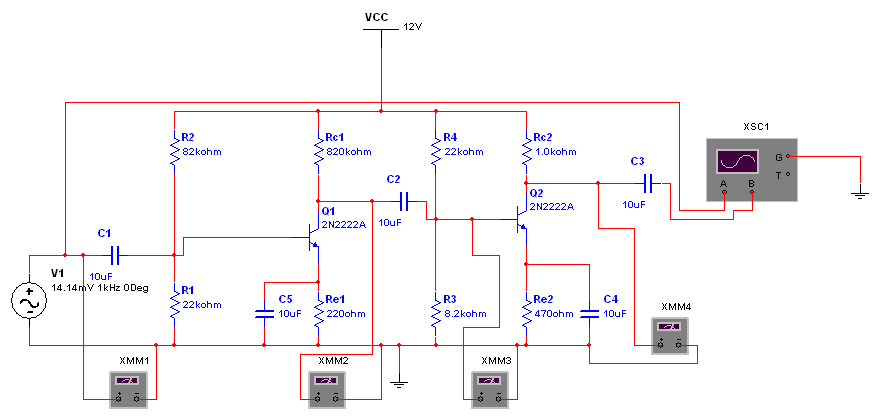

- Conecte un capacitor en paralelo con RE de la etapa de

entrada del mismo valor que el de la etapa de salida, como lo indica el

diagrama:

Figura 3:

Diagrama

de polarización del amplificador multietapa con dos transistores

bipolares, con un capacitor en paralelo con respecto a la resistencia

de emisor de la primera etapa

Figura

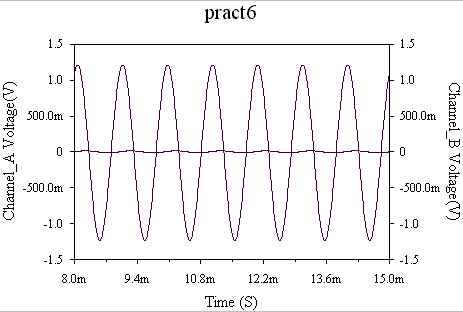

4:

Representación de la medición hecha en el

osciloscopio de las señales de salida y entrada del amplificador

Figura

4:

Representación de la medición hecha en el

osciloscopio de las señales de salida y entrada del amplificador

- ¿Qué sucede con la señal de

salida? Explique:

Como podemos ver

en la figura número 3; se colocó el capacitor en paralelo

como se indicó... al realizar la experimentación pudemos

ver dos cosas interesantes: 1) que la señal final de salida se

distorsionaba significativamente con esta nueva modificación en

el circuito; y 2) que, debido a ésto, la ganancia de voltaje

caía (no bruscamente, aunque sí significativamente). Sin

embargo, como se ve en la gráfica de la figura 4, otra vez la

simulación no nos refleja esta fenómeno en ningún

momento, aún así, confiemos en lo experimentado por

concordar de mejor manera con lo predicho por la teoría.

- Cuantifique la ganancia de voltaje y registre su valor.

La ganancia

estaba en el orden de los 16.

- Sustituya la etapa de amplificación de entrada del

circuito de la figura 1, por una a base de FET. Repitiendo el

procedimiento antes efectuado. Es indispensable rediseñar el

amplificador a las condiciones que usted requiera.

Rediseñando

el circuito, decidimos las siguientes condiciones para el amplificador:

Figura

5:

Diagrama

de polarización del amplificador multietapa con un transistor

monopolar en la etapa de entrada y uno bipolar en la etapa de salida

Figura

5:

Diagrama

de polarización del amplificador multietapa con un transistor

monopolar en la etapa de entrada y uno bipolar en la etapa de salida

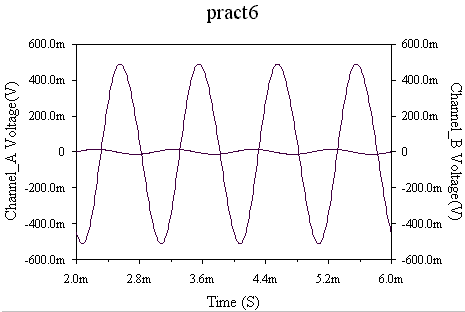

Obteniendo las siguientes simulaciones:

Figura 6: Representación

de la medición hecha en el

osciloscopio de las señales de salida y entrada del

amplificador, para el rediseño del amplificador con etapa de

entrada con FET

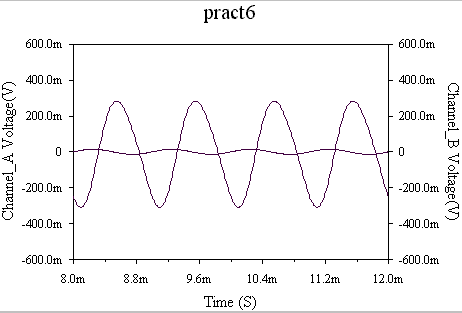

Figura 7: Representación

de la medición hecha en el

osciloscopio de las señales de salida y entrada del

amplificador, para el rediseño del amplificador con etapa de

entrada con FET y capacitor en paralelo con RS

Figura 8: Representación

de la medición hecha en el

osciloscopio de las señales de salida y entrada del

amplificador, para

el rediseño del amplificador con etapa de entrada con FET y con RS

= 1 K

Figura 9: Representación

de la medición hecha en el

osciloscopio de las señales de salida y entrada del

amplificador, para

el rediseño del amplificador con etapa de entrada con FET, con RD

= 1 K y C // RS

Analizando

el circuito en el experimento, se llegaron a varios hechos importantes:

- Que las mediciones de amplificación obtenidas no

concordaban en nada con lo esperado por las simulaciones (debido, sobre

todo a la falla en el acoplamiento entre fases de amplificación).

- La ganancia total del amplificador era de 30; mientras que la

ganancia de la primera etapa era de 16 y de la segunda se acercaba a

los 130; algo totalmente incongruente, que nos vuelve a indicar lo mal

acopladas que estaban ambas etapas.

- Conforme a los cálculos, no podíamos pasar de una

amplificación total de 26, aunque en la práctica se dio

un valor mayor.

- Por medio de experimentación "empírica" pudimos

notar cosas muy interesantes con respecto a la ganancia total y la

estabilidad, como es:

- Al

variar la RS, pudimos constatar que se seguía

conservando la misma relación que en el caso de la

variación de RE en un transistor bipolar: a menor

valor de esta resistencia, la ganancia del amplificador aumentaba,

aunque en este caso, la señal final no se distorsionaba.

- En

teoría se entiende que si RD

y Rent

de la segunda etapa son iguales, la transferencia de energía

resulta máxima; sin embargo ésto, llevado a la

práctica (y también pudiéndolo hacer

matemáticamente) no resulta completamente cierto... si seguimos

aumentando la RD

a un punto tal que RD>>Rent,

llegaremos a encontrar que el equivalente paralelo se acerca cada vez

más al valor de Rent,

por lo cual la transferencia sería mayor que si RD

=

Rent,

como es que siempre se ha manejado; sin embargo, este valor en RD

no puede ser demasiado grande, o todo el voltaje de la malla de salida

del FET caería por esta resistencia, por lo tanto, existe un

punto tal que ambos parámetros estén equilibrados.

- Al

aumentar la frecuencia de trabajo enormemente, comprobamos que el FET

tiene una mejor respuesta que cualquier transistor BJT.

- La

fase en ambas señales era la misma (aún y cuando en las

simulaciones no se apreciara lo mismo), debido al defasamiento de la

señal en ambos amplificadores; aunque la simetría no era

conservada como en otros circuitos (como se alcanza a ver, ligeramente,

en las simulaciones).

Arriba

Simulación

Las

representaciones mostradas en el apartado anterior.

Cuestionario

- ¿Cómo

definimos a un amplificador multietapa? Podemos

definir al amplificador multietapa como un arreglo de amplificadores

que se conectan en serie (cascada) y cuyas cargas en el primer

amplificador es la resistencia de entrada del segundo amplificador.

- ¿Para

qué nos es útil un arreglo de amplificador multietapa? Nos

es útil para amplificar una señal dada en varias

etapas, con ésto no corremos el riesgo (o al menos éste

es menor) de que la señal de salida esté distorsionada

o mal amplificada.

- ¿Es

necesario que las diferentes etapas de amplificación tengan

las mismas ganancias de tensión y de corriente? ¿por

qué? No,

no es necesario, porque cada etapa nos puede servir para un

propósito

en específico, por ejemplo, por lo general, las etapas

iniciales suelen ser amplificadores de tensión y la

última

o las dos últimas suelen ser amplificadores de corriente.

- ¿Cómo

podemos determinar la ganancia de una etapa? Ésta

se determina por la carga de ésta, que se gobierna por la

resistencia de entrada a la siguiente etapa.

- Para

casos de diseño, ¿es recomendable seguir un orden

determinado? ¿por qué? Si,

al diseñar (o utilizar) amplificadores multietapa, se debe de

iniciar en la salida y se continúa hacia la entrada, por lo

indicado en la pregunta anterior, es decir, calcular la ganancia de

una etapa, que está dada por la carga de dicha etapa.

- ¿Qué

diferencia hay de utilizar un transistor tipo FET en la primera etapa

de amplificación (también llamada de

pre-amplificación)

a utilizar un tipo BJT? En

principio, al tener una mayor impedancia de entrada, el FET nos

permite eliminar las señales de ruido que se encuentren junto

con la señal principal que alimente al amplificador; sin

embargo, debido a su naturaleza, presente una pequeña

distorsión de la señal que se genere a la salida.

- ¿Por

qué toma tanta importancia el valor de los capacitores de

acoplamiento en un arreglo de amplificador multietapa? Porque

dependiendo del valor de dichos capacitores será la respuesta

en frecuencia que tengan éstos con respecto a la impedancia

entre cada etapa de amplificación; por lo tanto, es

recomendable el tener un valor muy grande de capacitores para poder

considerarlos como “corto circuito”.

- ¿Por

qué es recomendable colocar el capacitor en paralelo con la

Resistencia de Emisor sólo en la última etapa de

amplificación? Porque

de colocarlo en etapas anteriores, podríamos provocar una

distorsión en la señal que entrara en la otra etapa de

amplificación, lo cual resulta indeseable.

- ¿Por

qué no colocar más etapas de amplificación

implementadas con transistores tipo FET dentro de un multietapa?

Debido

a la asimetría característica del FET, la

distorsión

de la señal sería mayor en cada etapa.

Conclusiones

Acosta

Valencia

Pablo.

En base a la práctica elaborada, a las

mediciones obtenidas y a los fenómenos observados, se puede

concluir que:

1.

Los acoplamientos en la

entrada del monoetapa con FET, hacen que la ganancia de voltaje en la

salida

del multietapa varie a tal grado que no corresponderá con la

ganancia del

monoetapa de salida.

2.

Al aumentar la frecuencia de

la señal de entrada, la señal de salida no se modifica,

es decir, no se va a

corte ni a saturación, debido a dichos acoplamientos con

capacitor.

3.

La resistencia

de entrada del

monoetapa con FET necesita ser grande con el fin de obtener mayor

ganancia a la

salida del multietapa.

Lozano López Jorge Andrés

En base a las

experiencias obtenidas a lo largo del desarrollo de esta

práctica (en donde

consideramos el diseño, armado y prueba del circuito), pude

darme cuenta de una

cosa muy importante: los detalles al momento de la

implementación de amplificadores

multietapa son muy importantes; hablar de desarrollo de fórmulas

a base de

parámetros híbridos es un punto complicado y la

bibliografía pertinente al

respecto de diseño por estos parámetros es muy diferente

entre éstos; por lo

tanto, la idea de homogeneizar dichos conceptos es un trabajo arduo.

Por otra

parte; todavía no se aplica (aunque se entiende en un grado

mucho mejor) el

concepto de acoplamiento como el factor más importante al

momento de la

amplificación; es necesario llevarlo a cabo para tener los

resultados lo más

parecidos en la práctica con respecto a lo calculado.

Ortíz

Morales

Daniel.

Por medio de esta

practica pudimos

observar que:

- Que al medir la ganancia de voltaje en el la 2da etapa

del

circuito amplificador fue mayor que la que obtuvimos en todas las

etapas esto

debido a la respuesta a la frecuencia de los capacitares y el

transistor BJT.

- Cuando aumentamos la frecuencia en el circuito

multietapa, la

señal no se vio afectada debido a los capacitores

acopladores.

- Observamos que el paralelo entre RD y RL debe ser

grande para un

ganancia mayor.

-

Aprendí

a utilizar los límites inferiores y superiores de Vp e

IDSS para poder calcular los valores de R1 y R2 por medio de la

gráfica.