那麼你的 analog inverter-type-amplifier 變成 digitial input buffer,

input buffer 需要 TTL-Compatible;

| 現代易學﹕ SPICE

SIMULATION 電算模擬實證 3rd Overtune XOC 八卦四象摩蕩網絡的定性及定量設計方法的神準正確性 |

現代易學﹕SPICE SIMULATION 電算模擬 實證 3rd Overtune XOC

八卦四象摩蕩網絡的定性及定量設計方法的神準正確性

[消遣調侃 Lcc Wizard]

我們一切看 結果 Result:

UNI SYSTEM 你說你的耶教文明西洋科學是科學﹐你設計結果﹐ SPICE

SIMULATE 不振盪﹔

UNI SYSTEM 你說我的中原文明八卦四象不科學﹐我設計結果﹐ SPICE

SIMULATE 會振盪﹔

UNI SYSTEM 說我不會用 SPICE﹐ 啊哈﹐ 出身 BERKELEY 的我曾寫過 SPICE

的核心程式.

UNI SYSTEM 詆毀唐明不會用 SPICE 的我﹐卻有世界上唯一的 XOC 的SPICE

simulate 的結果...

被搞迷糊的 Lcc Wizard ﹐ 你究竟相信那一個﹖

唐明嘆息﹕

政界沒有了規矩﹐七海不認九天也罷了﹔ 連學界也沒有了規矩﹐

UNI SYSTEM 狗眼看人低....

中原文明獨步古今﹕

到現在美國西方先進國家仍然無法用電腦模擬程式 SPICE

成功模擬 XTAL Oscillator Circuit(XOC) 的 Power-Up 時的 Ramp-Up 的過程﹗

這是 發展出 SPICE 的 UC Berkeley 積體電路權威 Meyer 所作的聲明﹗

這就是你為什麼在市面上買 XOC 設計的書﹐沒有一本書教你如何用

SPICE 來作設計的原因﹐而你也沒見過任何一個 XCO 的 SPICE simulation

的圖﹐正是應了矽谷名諺﹕“會作的﹐都賺錢去了﹔不會作的﹐就寫書”。

在這裡﹐矽谷“會作的”唐明展示 用 SPICE simulate XCO 的結果

以證明 中原尚國 的 八卦四象設計方法的正確性﹗

也就是 今天 Microprocessor 的 Clock Generator 的 核心 Reference Clock

仍然是在 “賭運氣”﹕

(1) 運氣好﹐可以振盪﹐用ON-CHIP的Inverter-Type-Amplifier(Analog Circuit)作XCO﹔

(2) 運氣不好﹐ 不能振盪﹐ON-CHIP 的 INVERTER 變成Input Buffer(Digital

Circuit),

另外買一個別家作的 XCO。

因為不能用 SPICE 作 Simulation 所以有這不確定性。

(3) 另外一種可能是 clock generator 在別的 Chip 上﹐ 你要用別人的 clock,

這時也是INVERTER 變成Input Buffer(Digital Circuit)。

這就增加了設計的困難度﹕

(I) CMOS input buffer 的 gain 較 Bipolar 小的很多﹔

(II) TTL compatible CMOS input buffer 更小﹔

(III) 1st order XCO 已很難振盪了﹔

(IV) 3rd order XCO 想都不要想﹗

但是﹐ 我們利用 中原文明的

八卦四象摩蕩網路發展出的定性及定量設計方法﹐

實證設計 XCO 證明 XCO 是可以用 SPICE 來 Simulate, 如果 你設計出來的不XCO

用SPICE來模擬﹐ 結果 不摩蕩振盪﹐

那你可要小心了﹐你的設計錯誤﹐

出來的 CHIP 會不振盪﹐ 你只好花錢買別家的 CHIP﹐ 想想就嘔﹐

不是嗎﹖

這些 SPICE SIMULATION 的附圖解說如下﹕

圖一﹕ TTL compatible input buffer : 萬一你的 XCO

不振盪﹐你只好外購 XCO﹔

那麼你的 analog inverter-type-amplifier 變成 digitial input buffer,

input buffer 需要 TTL-Compatible;

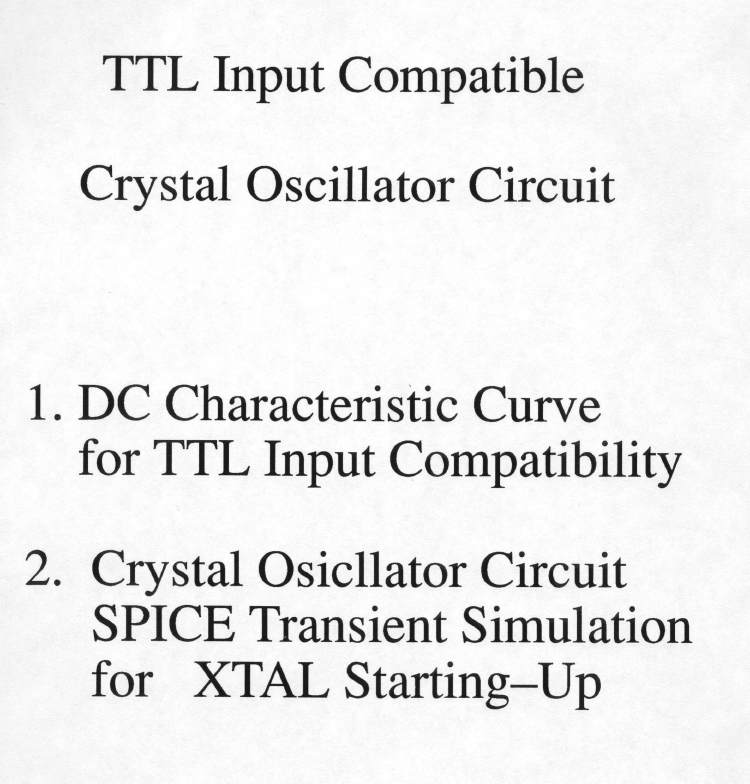

圖二﹕ TTL-compatible Input Buffer Schematics.

圖三﹕ TTL-compatible Input Buffer Characteristics.

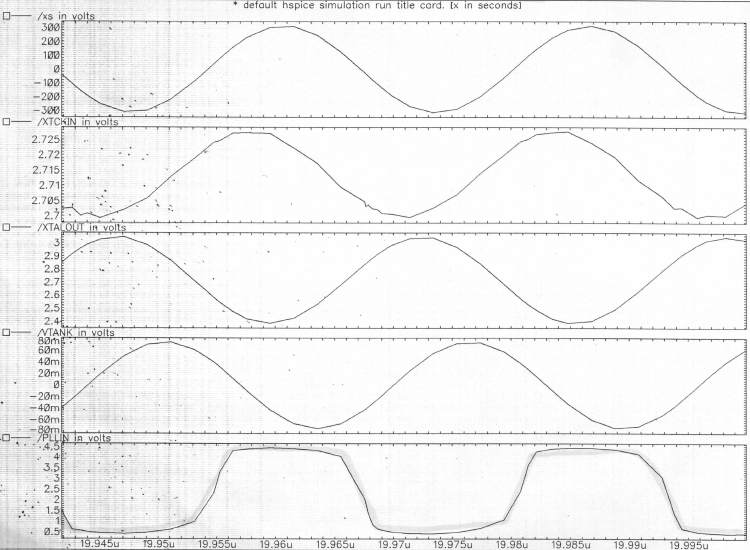

圖四﹕ XCO 的 振盪﹔ 5V power supply, 在 XTAL 內部 的

Voltage XS 居然可振到幾千 Volts.

圖五﹕ XCO 的 RAMP UP 過程。

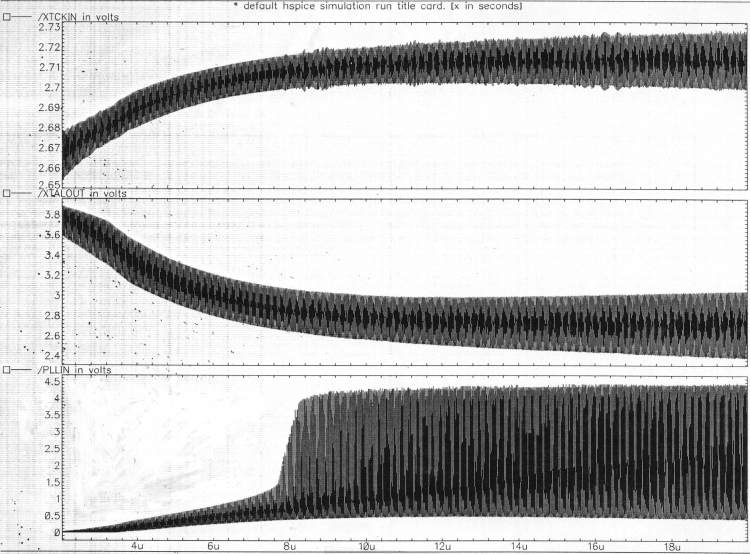

圖六﹕ 3rd Overtune XCO 的 艱困摩盪過程﹕

(0) 總圖﹔

(1) XTAL_IN 放大圖

(2) XTAL_OUT 放大圖

(3) PLL_IN 放大圖

唐明嘆息說﹕

這是我十多年前所作的﹐ 幸好我還有備份﹐

否則今天給 UNI SYSTEM 栽贓咬了一口﹐

而我拿不出任何 XCO SPICE simulation result﹐

我空口講白話﹐口說無憑﹐

我唐明是跳到黃河洗不清﹐但我唐明根本無所謂不在乎﹐

這也罷了﹐可恨的是﹐

卻是連中原文明聖學八卦四象兩儀太極的往聖絕學﹐

卻在我手中因我而遭 UNI SYSTEM 這種中原文明敗類作糟塌﹐

我是含恨莫名的﹗

-禍起蕭牆﹕Lcc Wizard 的家變﹗

網上現代版的“指鹿為馬”﹕指 XOC 為 VCO﹗

UNI SYSTEM: 你看看就好, 自個判斷是非...

Lcc Wizard: 連我都有點困惑了...

唐明﹕ UNI SYSTEM 他可以殺人﹐我不能跟著他殺人﹐

他可以胡扯 XOC 為 VCO﹐我不能跟他胡扯VCO...

>-----Original Message-----

>From: Lcc Wizard [mailto:[email protected]]

>Sent: Wednesday, June 14, 2000 9:20 AM

>To: 唐?

>Subject: Re: 現代易學:大大亟木、典制太極

>

>連我都有點困惑了...

>

>>From : Uni System 6:720/350 14 Jun 00

> To : Lcc Wizard 14 Jun 00

>23:45:05

> Subj : Re: 現代易學:大大亟木、典制太極

>

>你看看就好, 自個判斷是非...

>

>LW> [I] 幾乎所有的今天的SOC (System On Chip) 都是用 CMOS﹔

>LW> 純 NMOS chip 耗電量太大﹐吃不消﹗

>

>當然, 我是說 analog 的電路是用 n-mos, 數位電路才有可能是用 CMOS.

>他講類比電路, 我當然跟他扯類比電路. 而且, 現在大多是用 Bi-MOS

>電路來做, 因為純 MOS 要做定電流電路有實際的困難. ps.Pentium

>就是 Bi-MOS , 有 Intel 原廠資料可以看.

>ps2.Bi-MOS: Bipolayer-MOS , 這不是元件, 而是一種電路拓樸法.

>第一個陷井他就中了..

>

>LW> [II] 當然世界上沒有絕對是對 environment或溫度的 sensitivity

>LW> 不起變化效應的﹐ 只看大小而已﹐

>LW> XTAL 對 environment或溫度的 sensitivity 是比 電感電容

好的幾千萬倍....

>LW> 所以是用 XTAL 作基準去鎖定整個

摩蕩系統及振盪網路的頻率。

>LW> UNI SYSTEM 根本不在行﹐

>

>哈哈, 我就知道他會這麼講, 很可惜, 錯就是錯.

>對溫度最不敏感的是 X 切割, 你看看對 AT 切割及 Z 切割的 xtal

>對溫度敏不敏感. 還可以做精密的溫度測量,

您說他會不會受溫度影

>響? 笑笑..

>

>LW> 我已替 富士通﹐ AMD, National Semiconductor, NEC....

>. ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

>LW> 多少家設計 SOC﹐都是如此設計﹐ Intel Pentinum 的 Chip

>

>恕我直言, 這部份沒有人會做在 chip 裡, 除了 analog device,

>Intel Pentium 內部會有振盪器用的 Inverter ? 笑笑... 那外頻用

>的 PLL 都可以丟丟掉了...

>

>LW> 也是如此﹐ Inverter 一定是在 Chip 中而且是 CMOS circuit﹐

>LW> 這 Inverter 是 一個 analog circuit, 不是 digital circuit,

>LW> 是 amplifier; 而設計上﹐

> ~~~~~~~~~~~~

>Inverter 是 digital circuit, 有放大的功能, 不過這可以扯到類

>比, 您是第一個. 這是我第三個陷井.

[唐明嘆息﹕

什麼陷阱﹖是誰在裡面都還不知道呢﹗

也不怕風大閃了舌頭﹖

UNI SYSTEM 半調子就是半調子...

真是作法自斃﹐自暴其短...你不說別人不知道﹕

UNI SYSTEM 根本沒作過 analog circuit 設計...

連 INVERTER 在 XTAL OSSCIALTOR circuit

是 AMPLIFIER 是 ANALOG circuit

不是 DIGITAL CIRCUIT 這點最基本常識都沒有,

連 CIRCUIT 的 operating point 已設在 trigger point

都看不出來﹐....我都已講明了﹐還是“鴨子聽打雷”...

這就是證明了我當初開宗明義的說

連高科技矽谷敢碰 XTAL Oscillator Circuit 都沒有幾個....

要丟人現眼﹖..看誰是誰非..網上擂台賽見吧﹗

借此機會﹐

我也順便挑戰台灣科學園區 IC 設計人才﹐

看看新竹科學園區有無 設計高手﹖]

>LW> 給 user 用戶 可以作不同使用的 Configurations,

>LW> 如果用戶不用﹐另買整體的 XTAL OSCILLATOR 也可以,

>LW> 那麼這 inverter 就是 Buffer 而已﹐ 成了inverter 的 digital

circuit....

>LW> UNI SYSTEM 根本不在 IC 這一行﹐沒有必要再

>已經... 不知所云了喔, 我沒有做這行沒錯, 但我不會連基本的 IC

>怎麼使用都跟你一樣搞不清楚...

>

>你知道嗎? 我總共給他設了五個陷井,

兩個因為他不懂所以沒掉下去

>, 一是 SPICE, 這個從他沒有回信這點就可以看出他沒有玩過. 一是

>一開始我講他說的電路是 VCO, 很抱歉, 我講的是錯的! 不過他沒有

>指出, 可能他連 VCO 是什麼都不知道.. => Volute Control Osci-

>llator, 電壓控制振盪器, 講白一點跟他講的純 xtal 振盪電路是完

>全的無關.

>

>解釋一下他所說的 xtal 電路的走法:

>.

>........Interver...... 首先, 振盪的條件,

相位回授要為 0, 增

>..........|\.......... 益必須大於 1, Inverter 的地位是將相

>...----+--|.>o--+--.... 位反向 180' , 還有增益 (因為有 R1 當

>.......|..|/....|...... 回授, 電流 vs 電壓回授) , xtal 只有

>.......|........|...... 在他容許頻率內才會通過, 但相位相反!

>.......+--^_^_--+ R1... 也是 180' (領前) , 跟 Inverter 是不

>.......|........|...... 是剛好組合成 0' 的回授相位? 這樣才可

>.......|..|:`:|.|...... 以振盪. 當然, 不一定都可以回授的那麼

>.......+--|: :|-+ xtal 準確一定為 0, c1, c2 就是拉偏相位用

>.......|..|:.:|.|...... 的, 把回授回來的振幅相位修正為 0.

>......_|_......_|_.....

>......___ c1...___ c2

>........|........|......

>......###......###

[唐明嘆息﹕

UNI SYSTEM 你告訴我 R1 作什麼用的﹖

是 Inverter 的話﹐要 R1 作什麼﹖]

>這篇文章取自 Millman 4th (ps. 我前篇寫 4rd

是一個很顯眼的錯

>誤..) , no.21 other circuit device 篇有寫到. 今天又翻到一本

>翻自日本的書, 這個電路一樣可以做 VCO, 頻率漂移範圍極小而已..

>

>不想跟他扯太多, 去他的網站逛過一下之後發現他不但是個瘋子,

也

>是一個狂人, 狂的很徹底. 照片也不是他現在的照片,

今天提出他的

>錯誤論點, 他可以無止境的反擊,

內容是內行人一看就知道是斷章取

>義的解釋...

>所以, 他的東西能不能信, 自個判斷. 你有相信誰的自由.

[唐明嘆息]

在談XOC 時﹐我不提VCO﹐因為那是根本不相關﹐風馬牛不相及的事﹐

我不會上天下地﹐東拉西扯的亂扯...﹐

不要把不相關的事都拉進來﹐

那唬外行可以﹐在內行人眼中﹐胡扯什麼﹖

易經過去已一大堆人在胡扯了﹐

我今天就是在重建易學形象﹐

我不能跟他一樣胡扯﹐

他可以殺人﹐我不能跟著他殺人﹐

他可以胡扯VCO﹐我不能跟他胡扯VCO...

因為我只談XTAL Oscillator Circuit﹐

VCO 在 PLL 內﹐與 XTAL Oscillator Circuit 無關﹗

隔壁鄰居VCO 仍然是“外人”﹐

不是“XTAL OSCILLATOR”的“家人”﹐

把“外人”當“家人”來扯﹐胡扯什麼﹖

[0] 第一個﹐我談 SOC﹐ VLSI﹐是大型 Chip,

這些 chip 是把 digital, analog 全作在一塊 chip上﹐

而有 “mixed signal design" ...

[1] CMOS 的 Process 要在 chip 上﹐同時作 PMOS﹐ NMOS

masks 用的多﹐程序多, 成本高﹐yield 低, ....

這所以 過去 純 analog chip 為了省錢﹐減少製程才用 NMOS﹐

但在 VLSI 後 到今天 System-On-Chip,

digital circuit 一定是 CMOS 製程﹐

於是 analog 搭便車﹐ 成本問題不再是 算到搭便車的 analog

的頭上﹐所以﹐所有VLSI﹐ SOC的 analog 全改用 CMOS﹐而不是 NMOS﹐

CMOS analog 比 NMOS analog 好設計多了, 功能好多了。

尤其今天 LOW VOLTAGE design, NMOS analog 根本設計不出來﹐

全用 CMOS analog circuit 設計。

今天 Intel 用 BiCMOS那製程更貴了, Pentimum 一顆上千塊﹐

除了Intel 用得起﹐誰用得起﹖要不是跟 AMD 拼速度瘋了﹐ Intel

也不會用﹐

Intel 用 BiCMOS 是 Digital Output Buffer Ground Bounce 的問題﹐

不是 Digital OUTPUT BUFFER﹐ Intel 也不敢用 BiMOS,

還是乖乖的大家一起用 CMOS, 把 Digital Output Buffer 問題

因而用 BiMOS 扯蛋扯到 CMOS Analog circuit,

真會鬼扯蛋﹗

1.1

1978 我在 UCLA 就用 SPICE

1986 我在 National Semiconductor 作 Staff Analog Engineer

整天玩 SPICE 作 Simulation, 現在我是見了 SPICE 就想“吐”﹗

[2] 你想 賣 精密的 XTAL 都是笨蛋會切錯嗎﹖

我想買 “不精準”的 XTAL﹐ 都是“欲購無門”要

Special Order, 額外 charge﹐甚至對不起﹐

不接單﹐要改生產線﹐你老的生意鄙店不接...

否則整個好不容易精密 alignment 的生產線都全部 錯亂掉﹐

再等生產線穩定﹐已是兩個星期過去了﹐

[2] Clock Generator 的 Architecture 如下﹕

PLL 內的 VCO 是靠 XTAL OSSCILLATOR 作基準來鎖定﹐

.........................................................................

..............._____________________________________________.............

...............|..PLL.......................................|............

...............|.._______............_______.....______.....|...CLK_VCO_.

.________......|__|.....|..V_control.|.....|.....|.....|____|______......

.|.XTAL.|.CLK_REF.|.PD..|____________|.VCO.|_____|.NOV.|.................

.|..OSC.|_________|.....|............|_____|.....|_____|.................

.|______|.........|_____|................................................

.........................................................................

XTAL OSC: XTAL Oscillator

PLL : Phase Lock Loop

CLK_REF : Reference Clock 基準參考 clock

PD: Phase Detector

VCO : Voltage Controlled Oscillator

NOV : Non-Overlapping Clock Driver

2.1 我只談 XTAL Oscillator, 不談其他﹐ VCO 在 PLL 內﹐不在我討論範圍﹔

2.2 PLL 是用 PD 比較 CLK_VCO 的 與 CLK_REF 的 PHASE 差

而產生 V_control 去控制 VCO去產生 CLK_VCO

所以﹕

Jitter_CLOCK = Jitter_VCO + Jitter_XTAL

= Jitter_VCO = 0.2 ns (nano-second)

Jitter_XTAL ~ 0 (與 Jitter_VCO 比較太小﹐完全不計)

VCO 是最不準的東西﹐ 所有 “頻率漂移”都是由它而來﹐

為了不用 VCO﹐ RAMBUS 把 VCO 都除去而成為

DLL﹕ Delay Lock Loop!!!

2.3 拿 microprocessor chip 來﹐你看到兩個 pins

與 inverter 關係如下﹕

........ PIN......................................

........ CLK_IN ......|\..........PIN.............

..............X----+--| >o--+--X CLK_OUT(CLK_REF).

......................|/..........................

2.4 在作設計時﹐是整個 CLOCK GENERATOR 都交給你設計的﹐

我作 CLOCK GENERATOR 作的都想“吐”﹐

你想我不會知道那些名詞嗎﹖ 沒有必要拿來唬人

講明了是“定性”不是“定量”

我談的是由“易經觀點”來解析“XTAL Circuit" 只是

CLOCK GENERATOR 一小部份﹐

XTAL OSCILLATOR 內其中就有三個振盪網路﹐

這三個網路與VCO 一點關係都沒有﹗

他以為 180度 是天經地義﹐那是 “INVERTER I/O phase 180度的緣故﹐

我隨便換一個 circuit I/O 不是 180 相位﹐

那就不是這回事﹐

2.5 VCO 的 CIRCUIT 是什麼﹖ 我畫給你看﹕

就是 "RING OSCILLATOR" with "voltage controlled" "biasing

current source"

.......________________________________________________________..........

.......|....................VCO................................|.........

.......|.......................................................|.........

.......|.....|\ ......|\ ......|\ ......|\

.......|\ ..|.........

.......|--+--| >o----+--| >o---+---| >o---+---| >o-----+--| >o-|.........

.............|/ ......|/.........|/

......|/..........|/.............

............._|........._|........._|........._|.........._|.............

......_____||__________||_________||_________||__________||______________

V_control..||_.........||_........||_........||........._||_.............

..............|...........|.........|..........|...........|.............

.............GND.........GND.......GND........GND.........GND............

UNI SYSTEM, 我的 XTAL OSCILLATOR 有這樣的 VCO “"RING OSCILLATOR type"

circuit

嗎﹖ 沒有﹗那麼﹐在我談 XTAL OSCILLATOR 時﹐ 你瞎扯 VCO 作什麼呢﹖

2.6 在我的 XTAL Oscillator 內根本沒有V_control signal﹐

沒有V_control signal 那來的 Voltage-Controlled Oscillator?

UNI-SYTEM 引經據點的說﹕

>“這篇文章取自 Millman 4th (ps. 我前篇寫 4rd 是一個很顯眼的錯

> 誤..) , no.21 other circuit device 篇有寫到. 今天又翻到一本

> 翻自日本的書, 這個電路一樣可以做 VCO, 頻率漂移範圍極小而已..”

根本是“引諭失譬”﹐“錯把馮京作馬涼”“錯把 XOC 作 VCO”

真夠嗆的﹗

(XCO﹕ XTAL_OSCIALLATOR﹔ VCO﹕VOLTAGE-Controlled Oscillator)

2.7 UNI SYSTEM 在學術險道蘇花公路亂開飛車﹐結果摔得粉身碎骨﹐

唐明一看﹐就知道 UNI SYSTEM 的本事﹐不跟他的車﹐

我不跟UNI SYSTEM 的車到閻羅王那兒去報到﹐

不代表我不會開車﹗

唐明不跟 UNI SYSTEM 鬼扯蛋﹐不代表唐明不會學術...

2.8 唐明是世界首屈一指的 CLOCK GENERATOR 設計專家﹐

作到快吐2﹐我不用引經據典﹐書上都在胡說八道﹐

美國有矽谷網谷笑話的名言:

“會作的都跑去 Start-Up 賺錢去了﹐就只剩下不會作的才去寫書﹗”

UNI SYSTEM 拿那些“不會作”的人寫的書 在“會作”的唐明面前賣弄﹐

引經據典的﹐引用都引用錯了﹐

聽在有實戰經驗的唐明耳裡是半句話就只

UNI SYSTEM 沒有實戰經驗的講話一點feeling都沒有﹐全在鬼扯﹗

Lcc Wizard 怎麼找了這麼不上道的人﹖

要忍著耐性聽 UNI SYSTEM 鬼扯﹐真是很痛苦的一件事﹐

而且 UNI SYSTEM 一轉身﹐不說他不行﹐全是唐明的錯....

反被咬一口﹐...而大多數人都沒有這學術能力作判斷﹐

唐明真是啞巴吃黃蓮﹐....

更糟糕點是﹐“背後擺一道”﹐...唐明連怎麼死的﹐都不知道﹐...

這回要不是 Lcc Wizard 把 UNI SYSTEM 在我背後擺道的信

給我看﹐唐明又是重蹈 BERKELEY 覆轍﹐

怎麼被 CIA 擺道怎麼死的都不知道...

中國人的“與人為善”真會坑死人﹐弄得當事人一點抗辯的機會都沒有﹐

就被小人在後面說“悄悄話”給算計了﹗

要是當初 Earnest Kuh 能對 唐明說別人在他面前說什麼﹐

今天絕不會有台海大戰死傷百萬之局﹗﹗﹗﹗

有實戰經驗大唐明是根本不願跟“現代趙括”UNI SYSTEM 對話﹐

不但是怕沒品無格 UNISYSTEM 在後面說悄悄話暗中擺道﹐

更是不屑﹔

這就是解釋了不是

“趙括”兵學天下第一﹐而是為什麼有實戰經驗的

都不願跟 趙括 這個

沒實戰經驗的對話...鬼扯蛋扯的沒完沒了﹐ 趙括﹐你行﹐我怕你﹐

惹不起你﹐躲得起你總行了吧﹗結果徒負虛名的趙括坑趙卒40萬﹐

趙國人為趙括交“實戰”“學費”﹕為沒有實戰經驗的趙括

作了亡國滅族如此慘痛血淚代價付出﹗

唐明嘆息說﹕

UNI SYSTEM 你有在網上呱呱其談的本事﹐

就用 SPICE simulate 一個 CMOS XTAL OSCILLATOR 給我看...

我保證你鬼哭神嚎...作不出來...

2.9 你要看唐明的 3rd Overtune XTAL Oscillator circuit

SPICE Simulation 結果嗎﹖

可以﹐是你 UNI SYSTEM 把話說絕了﹕“唐明我把我十年前的 SPICE的Simulation

Result "Post" 在網上﹗

Lcc Wizard, 我今天晚上就 Email(詳見本網頁附件)

3. 總結﹐ 在 XTAL_OSCILLATOR 內﹐

有一個“八卦”層次的 摩“蕩”網路﹕那就是 XTAL_OSCILLATOR 本身﹔

有兩個“四象”層次的 振盪網路﹕

一是 串聯的 LC 振盪網路﹔

一是 並聯的 LC 振盪網路﹔

>-----Original Message-----

>From: Lcc Wizard

>Sent: Wednesday, June 14, 2000 9:33 AM

>To: 唐明

>Subject: 有沒有公司的網站

>有沒有您目前服務的公司的網站?

www.aptix.com ( www.eSoCverify.com

)

註:唐明的email為 [email protected]

附件:

圖一﹕ TTL compatible input buffer : 萬一你的 XCO

不振盪﹐你只好外購 XCO﹔

那麼你的 analog inverter-type-amplifier 變成 digitial input buffer,

input buffer 需要 TTL-Compatible;

圖二﹕ TTL-compatible Input Buffer Schematics.

圖三﹕ TTL-compatible Input Buffer Characteristics.

圖四﹕ XCO 的 振盪﹔ 5V power supply, 在 XTAL 內部

的 Voltage XS 居然可振到幾千 Volts.

圖五﹕ XCO 的 RAMP UP 過程。

圖六﹕ 3rd Overtune XCO 的 艱困摩盪過程﹕