1. Consiste en 8 registros de datos, 8 registros de direcciones, 2 apuntadores de pila, 1 contador de programa, y un registro de condición.

2. Desde el D0, hasta el D7. Y son de 32 bits.

3. Del A0, hasta el A6. Y son de 32 bits.

4. El MC68000 se encapsula con 64 pines, 23 para el bus de direcciones, 16 para el bus de datos, dos para la alimentación, dos para la tierra y el resto son pines de control.

5. Inmediato, Directo, Indirecto, indexado y Relativo.

6. Las instrucciones en lenguaje máquina del 68000 pueden incluir de una a cuatro palabras de 16 bits. La primera palabras contiene el codop y específica los modos de direccionamiento de los operandos a utilizar. En la palabra de codop pueden incluso especificarse direcciones cortas, tales como los nombres de los registros de la CPU. Para especificar inmediatamente operandos y direcciones de memoria se pueden utilizar palabras adicionales.

7. Mover un byte del registro de datos D1 al registro de datos D0.

8. Mover una palabra de M[ALFA] a M[A6 + 100016].

9. El 68020 es el primero en implementar 32 bits completos de la familia 68000

10. Ańadiendo nuevas características:

Tiene un bus de direcciones de 32 bits. De esta forma el 68020 puede direccionar 4 GB de especio de memoria en lugar de 16 Mb. Tiene un bus de datos de 32 bits. Esto significa que los datos de memoria pueden ser direccionados dos veces más rápido comparado con un procesador de 16 bits como el 68000 o el 68010. Incluye un memoria caché “ en chip”. Puede alojar a un coprocesador. Tiene vías de datos mejoradas. La ALU y todas las rutas internas tiene 32 bits.

11. El 68030es un más nuevo, poderoso y rápido microprocesador que el 68020. Las características del 68030 por encima del 68020 son: Más buses internos para que las direcciones y datos puedan ser procesados al mismo tiempo, la habilidad de activar o desactivar la UAMP por medio de software, un caché de instrucciones de 256 bytes y un caché de datos de 256 bytes que pueden ser accesados simultáneamente; dos segmentos transparentes que permiten a bloques sin trasladar, ser definidos por sistemas que transfieren grandes bloques de datos a direcciones predefinidas, como en aplicaciones de gráficas, arquitectura de vías con paralelismo aumentado que permite accesar desde cachés internos para trabajar en paralelo con transferencias de buses u instrucciones múltiples para ser ejecutadas conjuntamente, un controlador de buses mejorado que soporta ciclos asíncronos de buses, ciclos síncronos de buses que pueden operar en dos ciclos de reloj, y transferencias de datos pueden operar en un ciclo de reloj, todo con direcciones físicas.

12. Ya que incorporan:

Una unidad de enteros (Integer Unit) 68030 optimizada.

Una unidad de punto flotante (Floating-Point Unit) completa.

Caches más grandes.

Unidades de memoria separadas para instrucciones y datos.

13. Permite el estudio de un microprocesador RISC con coprocesador matemático y manejador de memoria virtual incorporados

14. Se accede a los elementos del arreglos en una sola instrucción, al igual que acceden otro tipo de estructuras de datos.

15. Se carga un programa especial en uno de los canales y la instruye para ejecutarlo. El canal maneja por sí mismo E/S de y hacia la memoria central, dejando libre la CPU para hacer otras cosas.

16. Es la seńal que se envía al microprocesador cuando se desea atender inmediatamente la atención de la CPU.

17. Para detener lo que este haciendo el procesador central y que pueda prestar atención al canal ocupado.

18. Para que el microprocesador pueda comunicarse directamente con sus dispositivos de E/S

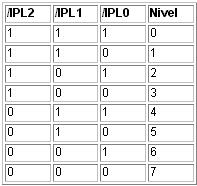

19. Existen 8 posibles niveles de interrupciones, que van desde el 0 (no petición) hasta el 7 (interrupción no enmascarable).

20. - IPL2, /IPL1, IPL0

21. Excepción de reset. Es la que se provoca al activar RESET y HALT de forma simultánea.

Errores de bus y de dirección. Un error de bus se produce cuando desde el exterior se activa la seńal BERR en un ciclo de memoria, y un error de dirección, cuando se intenta acceder con dirección impar a palabras o dobles palabras. En ambos casos se aborta el ciclo de memoria y se trata la excepción, no terminándose la instrucción.

Traza. Se provoca al final de una instrucción si está activo el bit de traza del registro de estado.

Interrupción. Se provoca al final de una instrucción si se solicita una interrupción por las líneas de interrupción IPL2, IPLA e IPL0, con una prioridad mayor de la actual.

Instrucción ilegal. Se provoca cuadno se intenta ejecutar un código de instrucción no implementado. Dos casos especiales son códigos de instrucción que empiecen con la secuencia 1111 ó 1010, que tienen vector específico.

Violación de privilegio. Se produce cuando se intenta ejecutar en modo usuario instrucciones que sólo se pueden ejecutar en modo supervisor.

TRAP. La propia instrucción TRAP provoca una de las 16 excepciones TRAP que expresa un operando inmediato.

TRAPO. Se provoca la excepción si ejecutando la instrucción CHK se detecta un desbordamiento de rango.

División por 0. Se provoca la excepción si en una instrucción de división el cociente es 0.

22. Algunas de las instrucciones nuevas proporcionan formas más eficientes de realizar ciertas operaciones, tal es como verificación de fronteras en arreglos, manejo de campos de bits, conversión de un byte a una palabra larga, empecado y desempacado de número BCD, retornos de procedimientos y sincronización de multiprocesadores.

23. Ninguna de éstas es en realidad esencial, pero los diseńadores de pastillas con frecuencia encuentra irresistible la idea de agregar nuevas instrucciones.

24. Algunas instrucciones del 68000 tienen una constante de 16 bits, por ejemplo, la distancia relativa entre la instrucción actual y la de ramificación. La mayoría de estas instrucciones se modificaron el 68020 y 68030 para permitir constantes de 32 bits. Excepto por los puntos seńalados aquí, los tres procesadores son iguales, para los programas usuario. Sin embargo, para el sistema operativo existen otras diferencias, en particular, en el manejo de las memorias principal y caché.

|