# Микропроцесорски системи 10. блок: Итерфејси за комуникацију SPI и I<sup>2</sup>C

др Срђан Митровић, дипл. инж.

зимски семестар, 2016./2017. год.

# Периферијски серијски интерфејс

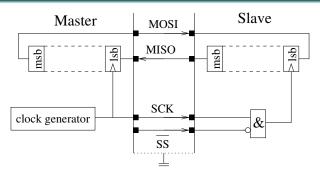

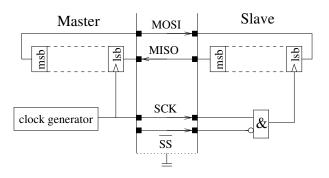

То је једноставан серијски *point-to-point* интерфејс заснован на *master-slave* принципу. Он омогућава *full-duplex* комуникацију између мастера (најчешће микроконтролер) и једног или више периферног уређаја (*slaves*).

# Интерфејс чине четири singleended линије:

- MOSI Master Out, Slave In. Ову линију користи мастер за предају података ка слејву.

- MISO Master In, Slave Out. Овом линијом слејв шаље податке мастеру.

- SCK System Clock. Мастер шаље слејву сигнал такта

- **SS** *Slave Select*. Овом линијом мастер селектује слејв.

## Периферијски серијски интерфејс

- интерни померачки регистар

- на сваки импулс такта msb мастера преко MOSI долази у регистар слејва као lsb

- ↑ на сваки импулс такта msb слејва преко MISO долази у регистар мастера као lsb

- после 8 циклуса, мастер и слејв су разменили поруке

## Периферијски серијски интерфејс

Мастер мора екпслицитно селектовати слејв постављајући  $\overline{SS}$  на "low". Могуће је поставити два слејва на SPI ако један директно реагује на  $\overline{SS}$ , а други прво негира линију. Уколико мастер може да користи више I/O пинова, број слејвова се може повећати на  $2^n$  употребом спољашњег декодера.

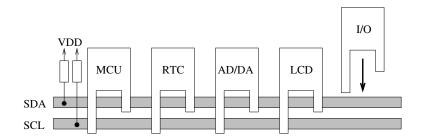

### Inter-IC Bus

- $I^2C$

- протокол је развио Philips <sup>1</sup>

- синхрона комуникација

- master slave принцип

- користи се за комуникацију на кратким растојањима

- може да фукционише у пет различитих модова:

- standard mode 100 kbit/s

- fast mode 400 kbit/s

- Fast mode Plus 1 Mbit/s

- highspeed mode 3.4 Mbit/s

- Ultra Fast-mode 5 Mbit/s (али је једносмеран)

- модови су компатибилни (осим последњег)

- дозвољено је постојање више мастера, а минимум је један

<sup>&</sup>lt;sup>1</sup>NXP Semiconductors . UM10204 I2C-bus specification and user manual. User Manual, 5, October 2012

$I^2C$

### Inter-IC Bus

- једноставно додавање нових уређаја на магистралу

- подржава 7-битно и 10-битно адресирање

- највиши битови (3 или 4) су хардверски резервисани (произвођач)

- адресе (0000XXX)<sub>2</sub> и (1111XXX)<sub>2</sub> су резервисане

- преостаје 112 могућих адреса за слејвове

- single-ended магистрала, напонски нивои су дефнисани у односу на масу:

- low level je y oncery  $\begin{bmatrix} -0, 5 & 0, 3 \cdot V_{DD} \end{bmatrix}$ V

- high level je y oncery  $[0, 7V_{DD} V_{DD} + 0, 5]V$

- позитивна логика

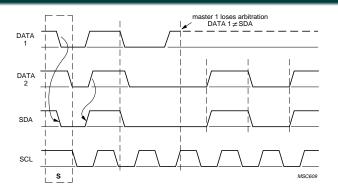

Пошто су жице повезане преко спољашних *pull-up* отпорника, *high level* се никада не успоставља. Ова асимтеричност између *low level* и *high level* узрокује то да линија има доминатно и рецесивно стање (*dominant and recessive state*). Уколико уређај да на излазу 0 и линија прелази у "ниско" стање, оно остаје ниско чак и ако један или више уређаја да на излазу "1".Пошто "0" увек побеђује, ова особина се зове и жичано И коло (*wired-AND*). Ова особина се користи у сврхе арбитрације.

- Неактивно стање је високо

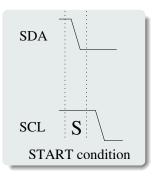

- Предају иницира мастер, стављањем сигнала такта на SCL и услова старта (S) на SDA линију.

- Мастер ставља адресу на магистралу и врсту приступа *R*/*W*.

- Након *R*/*W* бита *slave* шаље потврду да је препознао адресу.

- Шаљу се подаци, са потврдом након сваког бајта.

- На крају преноса, мастер генерише STOP (Р) и магистрала је слободна.

- или понавља START (Sr), завршава се текући пренос и почиње нови.

Inter-IC Bus

#### Start and Repeated Start

# СТАРТ и Поновљени СТАРТ

## Напомена

Само START и STOP мењају ниво на SDA док је SCL на "high". Нормалан ток података, укључујући и потврду – ACK, мења ниво када је стање на SCL "low".

Поновљени старт (Repeated Start) је исти као и обичан.

Address

### Адресе и управљање смером

## Адресе

Код 7-битних а дреса прво се шаље msb. SDA ниво се мења када је SCL на ниском нивоу, а чита се када је SCL на високом нивоу.

## Управљање смером – Direction Control

После 7 адресних битова, мастер завршава бајт слањем (R/W) бита који означава смер следеће трансмисије. Ако је R/W висок, мастер жели да чита податке, а ако је R/W низак мастер жели да шаље податке. Сваку трансмисију на магистрали започиње мастер, слањем адресе слејва, ако је R/W висок, слејв шаље потврду и мења се смер – слејв почиње са слањем података. Acknowledgement

# Acknowledgement

После сваких 8 битова пријемник шаље потврду –  $(\overline{ACK})$  да је примио податке. Потврда се шаље постављањем SDA на "low". Једини изузетак је последња потврда када је мастер пријемник: тада мастер не потврђује последњи бајт и SDA остаје "high", што сигнализира слејву који предаје податке да је пренос завршен. Слејв ослобађа линију и чека поновљени старт или стоп.

## Data

Битови података се шаљу као и остали битови, и сваки бајт се мора потврдити од стране пријемника. Прво се шаље msb бит. Не постоји ограничење броја битова података у једном фрејму предаје.

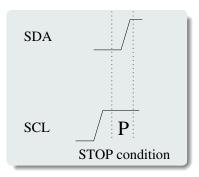

# STOP

Сигнал STOP (P) је супротан услову START, сада се SDA поставља са "low" на "high" када је SCL "high". Стоп шаље мастер када жели да ослободи магистралу. Чим је STOP послат, магистрала је неактивна (idle) и може је захтевати неки други мастер.

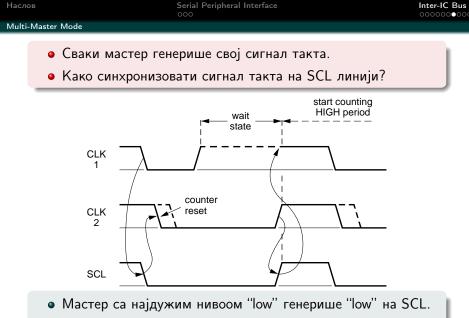

• Мастер са најкраћим нивоом "high" генерише "high" на SCL.

• wired-AND

### Bus Arbitration

# • Како одредити ком мастеру доделити SDA линију?

• Користи се wired-AND особина SDA линије.

Inter-IC Bus

#### Bus Arbitration

- Када је магистрала неактивна (idle), било који мастер може послати старт и почети трансмисију.

- Мастер проверава стање SDA линије (да ли је послати бит постављен на линији).

- Низак ниво је доминантан, мастер који уписује 1 и чита 0 препознаје да је магистрала заузета.

## Домаћи – необавезан – топло се препоручује

Направити табелу проучаваних комуникационих протокола и интерфејса сортираних по броју линија које се користе за комуникацију. Линију GND не бројати. У додатним коланама описати: синхрона, асихрона, серијска, паралелна, full duplex, half duplex...